# Hardware Verification Using Theorem Proving and SMT/SAT Solving

Yan Peng<sup>1</sup>

<sup>1</sup>Department of Computer Science University of British Columbia

November 7th 2018

- Motivation

- 2 Smtlink

- 3 AMS Verification

- Asynchronous Circuit Verification

- 6 Glitch Hunting

- **6** The Exciting Future Work

## The Quest of FV of Timed/Continuous Systems

- Formal verification for digital circuits involving only discrete states has been extensively researched

- Formal verification for timed and continuous systems is less mature than formal verification of digital hardware

- Huge area of applications: chip designs, robotics, autonomous cars, neuromorphic chip designs and other cyber-physical systems

- 2 Reachability analysis

- over-approximation can be too large, refining over-approximation might lead to run-time and memory issues

- ② Usually the analysis start with a fixed set of parameters

## Bridging Theorem Proving and SMT/SAT Solving

- We revisit the rigorous approach of using theorem proving and aim to analytically verify timed and continuous systems

- Can prove a system for a range of parameters

- Open't have the over-approximation problem

- Our designers are not going to learn these theorem provers ..."

- Oue to good reason ... theorem proving requires excessive manual work, and ... expertise

- We address this problem by combining theorem proving with SMT/SAT solving

- Theorem provers serve as a problem and property modeling system and induction proof engine

- SMT/SAT solvers crack out the details in large flattened lemma instances

- Motivation

- 2 Smtlink

- 3 AMS Verification

- 4 Asynchronous Circuit Verification

- 6 Glitch Hunting

- **6** The Exciting Future Work

#### The ACL2 Theorem Prover

- A Computational Logic for Applicative Common Lisp

- The ACL2 theorem prover is both interactive and automatic

- ACL2 uses a subset of Common Lisp, which allows serious programming

- The use of clause-processors, computed hints, meta-extract to allow logically sound extensions of the theorem prover

- ACL2 emphasize large system verification and has various language supports for improving performance

#### **Smtlink**

ACL2::projects

#### **Smtlink**

[books]/projects/smtlink/doc.lisp

SMT Package

Tutorial and documentation for the ACL2 book, Smtlink.

#### Introduction

A framework for integrating external SMT solvers into ACL2 based on the ACL2::clause-processor and the ACL2::computed-hints mechanism.

#### Overview

Smtlink is a framework for representing suitable ACL2 theorems as a SMT (Satisfiability Modulo Theories) formula, and calling SMT solvers from within ACL2.

A sound framework for integrating SMT solvers into the ACL2 theorem prover.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>Y. Peng and M. R. Greenstreet. "Smtlink 2.0". In: 15th International Workshop on the ACL2 Theorem Prover and Its Applications (ACL2-2018). 2018.

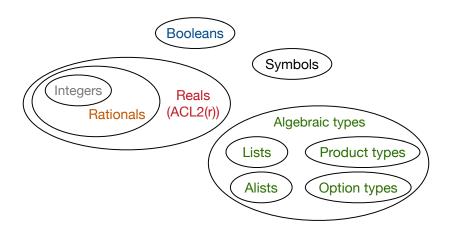

#### What's Supported in Smtlink

These cover a moderate amount of datatypes that are required for modeling systems

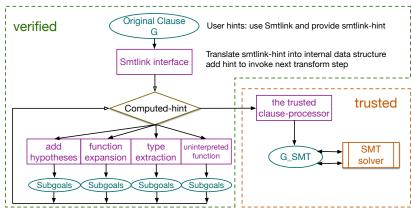

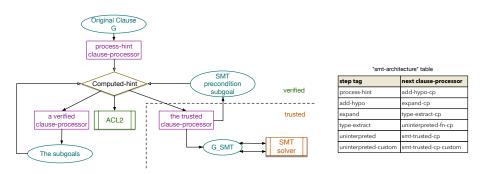

#### The Architecture

## The architecture is both extensible and has a compelling argument for soundness

Verified clause-processors transform ACL2 goal into SMT theories. Each verified clause-processors adds a hint indicating which step to take next.

#### The Architecture - Cont'd

- Each step is a verified clause-processor that can be configured through a single table

- Only the last step uses a trusted clause-processor

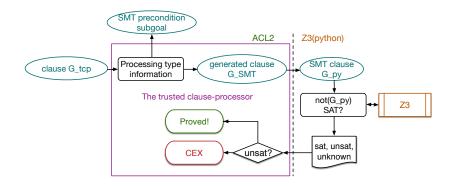

#### The Trusted Clause Processor

- What's not verified? The trusted clause-processor, Z3py interface class, and Z3

- SMT precondition subgoals: subgoals that have to be satisfied to ensure soundness.

#### Counter-example Generation

|                   | asymtay ayamala ayamalas                                |  |  |  |

|-------------------|---------------------------------------------------------|--|--|--|

| types             | counter-example examples                                |  |  |  |

| booleans          | ((X NIL))                                               |  |  |  |

| integers          | ((X 0))                                                 |  |  |  |

| rationals         | ((X 1/4))                                               |  |  |  |

| algebraic numbers | ((Y (CEX-ROOT-OBJ Y STATE (+ (^ X 2) (- 2)) 1)) (X -2)) |  |  |  |

| symbols           | ((X (SYM 0)))                                           |  |  |  |

| lists             | ((L (CONS O (CONS O NIL))))                             |  |  |  |

| alists            | ((L (K SYMBOL (SOME 0))))                               |  |  |  |

| product types     | ((S2 (SANDWICH 0 (SYM 2))) (S1 (SANDWICH 0 (SYM 1))))   |  |  |  |

| option types      | ((M2 (SOME 0)) (M1 (SOME 0)))                           |  |  |  |

- Algebraic numbers are represented by the k<sup>th</sup> root of some polynomial

- ② The (K s v) for alists represents an array mapping any values of s sort/type into a constant value (or an expression) v.

- Currently evaluable counter-examples are booleans, integers and rationals

#### Summary

#### In summary,

- I built a novel sound framework for integrating the Z3 SMT solver into the ACL2 theorem prover

- There are several highlights of Smtlink:

- This framework itself is mostly verified, leading to a compelling argument of soundness

- It supports a substantial number of datatypes and SMT theories, therefore can find use in a large number of applications

- Counter-examples are returned back into the ACL2 theorem prover for further scrutiny

- Coming together with ACL2 available at: https://github. com/acl2/acl2/tree/master/books/projects/smtlink with documentation at:

http://www.cs.utexas.edu/users/moore/acl2/manuals/

current/manual/?topic=SMT\_\_\_\_SMTLINK

- Motivation

- 2 Smtlink

- 3 AMS Verification

- Asynchronous Circuit Verification

- 6 Glitch Hunting

- **6** The Exciting Future Work

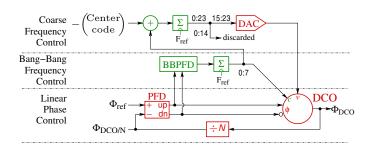

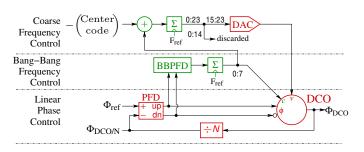

## The digital Phase-Locked Loop example [CNA10]

- A PLL is a feedback control system that, given an input reference clock  $f_{ref}$ , it outputs a clock at a frequency  $f_{DCO}$  that's N times of the input clock frequency and aligned with the reference in phase.

- Analog/Mixed-Signal design are composed of both analog and digital circuits.

## The digital Phase-Locked Loop example [CNA10]

- We published an early version of this proof<sup>2</sup> using two approaches hybrid automaton and Lyapunov functions:

- Main limitation with hybrid automaton: Reasoning about a fixed design

- Main limitation with Lyapunov approach: model is simplified <sup>2</sup>J. Wei et al. "Verifying global convergence for a digital phase-locked loop". In: 2013 Formal Methods in Computer-Aided Design. 2013, pp. 113–120. DOI: 10.1109/FMCAD.2013.6679399.

### Modelling the digital PLL

• The digital PLL is naturally modelled using non-linear recurrences that update the state variables on each rising edge of  $\phi_{ref}$ .

$$c(i + 1) = next_c(c(i), v(i), \phi(i))$$

$v(i + 1) = next_v(c(i), v(i), \phi(i))$

$\phi(i + 1) = next_\phi(c(i), v(i), \phi(i))^3$

<sup>&</sup>lt;sup>3</sup>Three state variables: capacitance setting c (digital), supply voltage v (linear), phase correction  $\phi$  (time-difference of digital transitions).

#### Modelling the digital PLL

In more details,

```

\begin{array}{rcl} & c(i+1) &=& \mathsf{saturate}(c(i) + g_c \, \mathsf{sgn}(\phi(i)), c_{\mathsf{min}}, c_{\mathsf{max}}) \\ & v(i+1) &=& \mathsf{saturate}(v(i) + g_v(c_{\mathsf{center}} - c(i)), v_{\mathsf{min}}, v_{\mathsf{max}}) \\ & \phi(i+1) &=& \mathsf{wrap}(\phi(i) + (f_{\mathsf{dco}}(c(i), v(i)) - f_{\mathsf{ref}}) - g_\phi\phi(i)) \\ & f_{\mathsf{dco}}(c, v) &=& \frac{1+\alpha v}{1+\beta c} f_0 \\ & \mathsf{saturate}(x, lo, hi) &=& \mathsf{min}(\mathsf{max}(x, lo), hi) \\ & \mathsf{wrap}(\phi) &=& \mathsf{wrap}(\phi+1), & \text{if } \phi \leq -1 \\ &=& \phi, & \text{if } -1 < \phi < 1 \\ &=& \mathsf{wrap}(\phi-1), & \text{if } 1 \leq \phi \end{array}

```

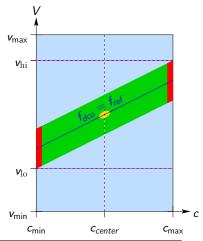

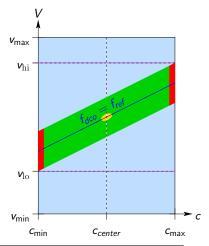

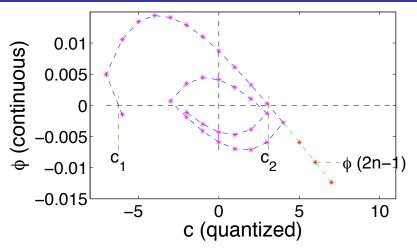

## The Convergence Proof<sup>3</sup>

The global convergence property:

$$\exists N, \forall [c(0), v(0), \phi(0)] \in B,$$

$$\forall i \ge N, [c(i), v(i), \phi(i)] \in Y$$

In English: There exists a time bound such that for any initial state, the digital PLL reaches the final convergence region within that amount of time.

<sup>3</sup>Yan Peng and Mark Greenstreet. "Integrating SMT with Theorem Proving for Analog/Mixed-Signal Circuit Verification". In: *NASA Formal Methods*. 2015.

## The Convergence Proof<sup>3</sup>

The convergence can be formulated using four lemmas:

- Coarse convergence: blue region to red and green region – Z3

- Leaving saturation: red region to green region – Z3

- Fine convergence: green region to yellow region – Smtlink 1.0

- Invariant: yellow region is invariant

<sup>3</sup>Yan Peng and Mark Greenstreet. "Integrating SMT with Theorem Proving for Analog/Mixed-Signal Circuit Verification". In: *NASA Formal Methods*. 2015.

## Fine Convergence

- Requires reasoning about sequences of states.

- $\bullet$  We proved that each crossing of  $\phi=0$  is closer to the origin than the previous one.

### An example from the DPLL proof

Definitions:

$$\begin{aligned} & \texttt{B-term(h)} = & (1-K_t)^{-h} (\mu \frac{1+\alpha(d_0+d_v)}{1+\beta(g_1h+(equ_c\ v_0))}-1) \\ & \texttt{B-sum(n)} = & \sum_{h=1}^n (\texttt{B-term}(h)+\texttt{B-term}(-h)) \end{aligned}$$

#### An example from the DPLL proof

#### Key lemmas proved:

```

(defthm B-term-neg

(implies (and (dpll-hyps :g1 :Kt :v0 :dv :pos h)

(nc-ok h (- h)))

(< (+ (B-term h v0 dv g1 Kt) (B-term (- h) v0 dv g1 Kt)

) 0))

:hints (("Goal","

:smtlink-custom

(:hypotheses (((implies (<= 2 h)

(<= (expt (gamma Kt) h)

(expt (gamma Kt) 2)))))))

:rule-classes :linear)

(defthm B-sum-neg

(implies (and (dpll-hyps :g1 :Kt :v0 :dv :pos n-minus-2)

(nc-ok (- n-minus-2)))

(< (B-sum n-minus-2 v0 dv g1 Kt) 0))

:hints (("Goal" :in-theory (e/d (B-sum) (B-term)))))

```

- Motivation

- 2 Smtlink

- 3 AMS Verification

- Asynchronous Circuit Verification

- 6 Glitch Hunting

- **6** The Exciting Future Work

#### Motivation

- Asynchronous design offers many advantages:

- 1 It works when a design has more than one timing domain

- In some cases asynchronous designs can be faster or simpler than their synchronous counterparts

- Problem is naturally event-driven: neuromorphic chip design

- ② But asynchronous circuits are more intellectually challenging to understand

- The exact ordering of events is not statically determined; thus, asynchronous designs are also non-deterministic

- We want to be able to verify safety and liveness properties of asynchronous circuits

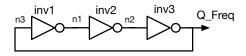

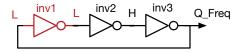

## The Simple Ring Oscillator Example

- A ring oscillator is an oscillator circuit consisting of an odd number of inverters in a ring

- A 3-stage ring oscillator consists of three inverters

- The one-safe property:

#### Theorem (One-Safe)

Starting from a state where there is exactly one inverter ready-to-fire, for all future states, the ring oscillator will stay in a state where there is only one inverter ready-to-fire.

### The Simple Ring Oscillator Example

- A ring oscillator is an oscillator circuit consisting of an odd number of inverters in a ring

- A 3-stage ring oscillator consists of three inverters

- The one-safe property:

#### Theorem (One-Safe)

Starting from a state where there is exactly one inverter ready-to-fire, for all future states, the ring oscillator will stay in a state where there is only one inverter ready-to-fire.

#### The Simple Ring Oscillator Example

- A ring oscillator is an oscillator circuit consisting of an odd number of inverters in a ring

- A 3-stage ring oscillator consists of three inverters

- The one-safe property:

#### Theorem (One-Safe)

Starting from a state where there is exactly one inverter ready-to-fire, for all future states, the ring oscillator will stay in a state where there is only one inverter ready-to-fire.

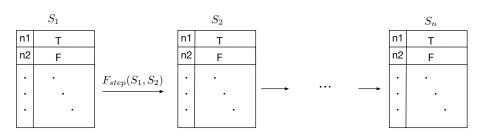

## Modeling the Ring Oscillator

- We model circuits using trace recognizers (based on [Dil87])

- A state is an alist mapping from signal paths to its state value

- A stepping function constrains possible next state; allows nondeterministic behaviors

- A trace is a list of states

#### The Theorem

- ringoc3-one-safe-lemma: the inductive step proved using Smtlink

- Smtlink expands out definitions and z3 is able to derive enough relationships between terms to figure out the proof

- Smtlink is very good at flattened formulas with large amount of details

## Extend the Proof to Arbitrary Number of Stages

- We've proven a theorem that states the one-safe property with a ring oscillator of arbitrary number of stages

- Some statistics of the proof:

| FTY types | Functions | Total thms | Smtlink thms | LOC  |

|-----------|-----------|------------|--------------|------|

| 5         | 17        | 55         | 23           | 2375 |

- Smtlink is smarter than I thought it was

- There are still potential of improvements

- Much of the lengthiness of the proof is coming from having to expand terms out enough, so that Smtlink can handle the proof

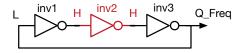

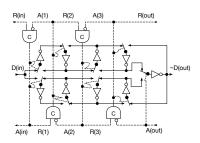

## The Micropipeline [Sut89]

- This is a timed-circuit: the correctness depends on the inverters propagating data values faster than the C-elements propagating control events

- We've verified that the control path of a single stage micropipepline is one-safe

- We plan to verify safety and functional correctness of the FIFO in the near future using trace theory as is used for the ring oscillator

- Motivation

- 2 Smtlink

- 3 AMS Verification

- Asynchronous Circuit Verification

- 6 Glitch Hunting

- **6** The Exciting Future Work

#### Motivation

- Chip designs commonly contain multiple clock domains, multi-cycle paths, test circuits with long logic delays

- Synthesis tools are based on circuit models that ignore the possibility that signals from other clock domains can change at arbitrary times

- Glitch bugs are hard to find, nearly impossible in simulation

Have to do frequency sweeping

- This is a bug that has been found in real designs

- The work shown here are published results in a paper in ASYNC2016 and a poster in DAC2018

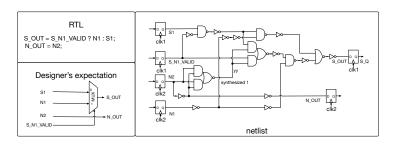

## Synthesis-generated Glitch

**Glitch**: a transition on a non-synchronous signal can cause the output of the combinational logic to temporarily change to an unstable value.

**Synthesis-generated Glitch**: synthesis tools can introduce glitches. This can happen even though the RTL design is free of such a glitch.

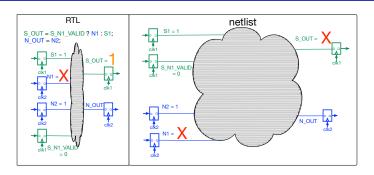

#### Is the netlist equivalent to the RTL?

- YES! When using standard logical-equivalence checking

- Logical equivalence formulation:

"For every input from {T, F}, the netlist produces the same output as the RTL."

- Signal naming:

- S signals Synchronous to output clock domain

- N signals Non-synchronous to output clock domain

# Glitches caused by non-synchronous signals

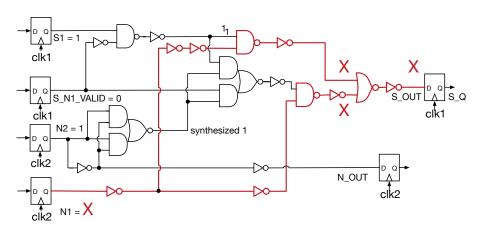

- Standard logical-equivalence is not enough, e.g., when S N1 VALID is 0:

- RTL: permits only S1 to pass to the MUX output, S\_OUT

- netlist: allows a glitch to propagate from N1 to S\_OUT

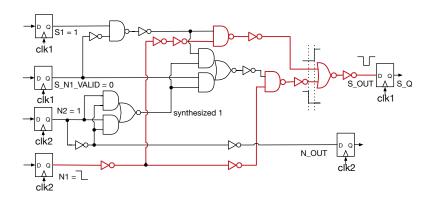

# Using ternary simulation to detect glitch

• Ternary logic values {T, F, X} facilitate detection of glitch paths

## The Formal Definition

• For a state-bit, q, let  $\mathcal{S}_q$  denote the synchronous inputs to the combinational logic for the next-state of q, and  $\mathcal{N}_q$  denote the non-synchronous inputs. Let  $\mathbb{B} = \{0,1\}$ , and  $\mathbb{B}^{\mathbf{X}} = \{0,1,\mathbf{X}\}$

glitchFree(q) =

$$\forall S_q \in \mathbb{B}^*$$

.  $\forall \mathcal{N}_q \in \mathbb{B}^{\mathbf{X}^*}$ .

$(\text{next}_{q,\text{net}}(S_q, \mathcal{N}_q) = \mathbf{X}) \Rightarrow (\text{next}_{q,\text{RTL}}(S_q, \mathcal{N}_q) = \mathbf{X})$  (1)

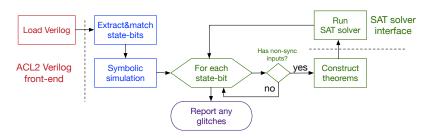

# Sequential Glitch Hunter<sup>4</sup>

- ACL2 provides a comprehensive Verilog front end and a SAT solver interface

- Theorems are automatically constructed and proved for all statebits

- When a glitch is found, a counter-example is shown indicating the glitch inputs

<sup>4</sup>Y. Peng, I. W. Jones, and M. R. Greenstreet. "Finding Glitches Using Formal Methods". In: 2016 22nd IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC). 2016.

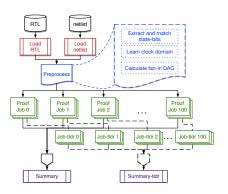

## Parallel Glitch Hunter

- distribute computation over multiple machines by leveraging the ACL2 certification method and the Unix Make utility

- Fault-tolerant parallel runs

- Other performance improvements: fast-alists (i.e. applicative maps backed by hash tables), memoization and guards

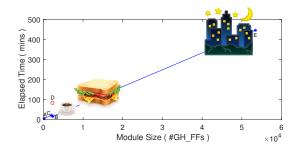

# Experimental Results

Table: Modules and Run Time

| Module   | #gates | #FFs   | #GH-FFs <sup>a</sup> | $T_{32}^{\ b}$ | $T_{\min}^{c}$ | $P_{\min}^{d}$ |

|----------|--------|--------|----------------------|----------------|----------------|----------------|

| Module A | 1264   | 721    | 221(30.7%)           | 6              | 6              | 16             |

| Module B | 10923  | 4256   | 2378(55.9%)          | 17             | 13             | 96             |

| Module C | 90432  | 14874  | 2045(13.7%)          | 22             | 20             | 96             |

| Module D | 29018  | 5092   | 2293(45.0%)          | 84             | 84             | 32             |

| Module E | 238783 | 177996 | 53415(30.0%)         | 446            | 280            | 100            |

<sup>&</sup>lt;sup>a</sup>GH-FFs are state-bits that include non-synchronous inputs in their fan-in trees

<sup>&</sup>lt;sup>b</sup>Time (in minutes) with 32 parallel jobs

$<sup>^{</sup>c}T_{min}$  is the fastest run (in minutes) for the module

$<sup>^</sup>dP_{\min}$  is the number of processors for the fastest run

# Experimental Results - Cont'd

- For modules with a few thousand gates, the time to dispatch jobs dominates, and 16 or 32 processors seems optimal

- Por modules with hundreds of thousands of gates, the preprocessing step is a sequential bottleneck accounting for about 2% of the total computation and limiting speed-up to around 50

- Outlier module D for preprocessing time due to combinational loops

- Motivation

- 2 Smtlink

- 3 AMS Verification

- Asynchronous Circuit Verification

- 6 Glitch Hunting

- 6 The Exciting Future Work

# The Exciting Future Work

- Short term:

- For Smtlink, we want to add reflection and type inference

- We are interested in applying Smtlink to several asynchronous designs

- Formally verify Sutherland's micropipepline

- The verification of an initialization problem of an deskew ASP\* FIFO

- Long term: I'm very interested in applying Smtlink to software problems.

- Obstributed systems: bares similarities to asynchronous circuits

- Machine learning algorithms: convergence of various versions of stochastic gradient problems

## Conclusion

Conclusion: we showed how combining theorem proving and SMT/SAT solving have great potential in verifying timed and continuous systems.

- We have built a novel connection of SMT solvers into the theorem prover ACL2, called Smtlink

- We verified convergence of a digital Phase-Locked Loop and plan to reason about asynchronous circuits in the near future using Smtlink

- Ouring my internship at Oracle, I applied a similar idea of using the ACL2 theorem prover and SAT solvers for solving an industry problem of detecting synthesis-generated glitches

## Questions?

## Maybe you should consider asking Smtlink that question? ...

ACL2::projects

#### **Smtlink**

[books]/projects/smtlink/doc.lisp

SMT Package

Tutorial and documentation for the ACL2 book, Smtlink.

#### Introduction

A framework for integrating external SMT solvers into ACL2 based on the ACL2::clause-processor and the ACL2::computed-hints mechanism.

#### Overview

Smtlink is a framework for representing suitable ACL2 theorems as a SMT (Satisfiability Modulo Theories) formula, and calling SMT solvers from within ACL2.

## References I

J. Crossley, E. Naviasky, and E. Alon. "An energy-efficient ring-oscillator digital PLL". In: *Custom Integrated Circuits Conference (CICC), 2010 IEEE.* 2010, pp. 1–4. DOI: 10.1109/CICC.2010.5617417.

David L. Dill. "Trace Theory for Automatic Hierarchical Verification of Speed-independent Circuits".

AAI8814716. PhD thesis. Pittsburgh, PA, USA: Carnegie Mellon University, 1987. URL: http://reports-archive.adm.cs.cmu.edu/anon/scan/CMU-CS-88-119.pdf.

Yan Peng and Mark Greenstreet. "Integrating SMT with Theorem Proving for Analog/Mixed-Signal Circuit Verification". In: NASA Formal Methods. 2015.

## References II

Y. Peng and M. R. Greenstreet. "Smtlink 2.0". In: 15th International Workshop on the ACL2 Theorem Prover and Its Applications (ACL2-2018). 2018.

Y. Peng, I. W. Jones, and M. R. Greenstreet. "Finding Glitches Using Formal Methods". In: 2016 22nd IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC). 2016.

I. E. Sutherland. "Micropipelines". In: Commun. ACM 32.6 (June 1989), pp. 720–738. ISSN: 0001-0782. DOI: 10.1145/63526.63532. URL: http://doi.acm.org/10.1145/63526.63532.

## References III

J. Wei et al. "Verifying global convergence for a digital phase-locked loop". In: 2013 Formal Methods in Computer-Aided Design. 2013, pp. 113–120. DOI: 10.1109/FMCAD.2013.6679399.

# There are Always Exceptions - Precondition Example

```

(fty::deflist intlist

:elt-type integerp

:true-listp t)

(defthm bogus

(implies (intlist-p x)

(or (< (car x) 0)

(equal (car x) 0)

(> (car x) 0)))

x = \text{nil} is a counter-example to this bogus theorem:

let x = nil:

(or (< (car nil) 0) (equal (car nil) 0) (> (car nil) 0))

(car nil) = nil:

(or (< nil 0) (equal nil 0) (> nil 0))

All comparisons of non-numbers produce nil:

(or nil nil nil) = nil

```

## Precondition Example Cont'd.

A direct translation of the ACL2 goal:

But x = nil is not a counter-example to this Z3 theorem. Because IntList.car(nil) in Z3 denotes an arbitrary integer value, and the theorem trivially holds.

# Precondition Example Cont'd.

### The problem:

- ACL2: Taking car of nil gives us nil

- Z3: Taking car gives us an arbitrary value of the appropriate type

Solution: add precondition check  $x \neq nil$  in places where (car x) is applied;

```

Similarly, for (cdr (assoc-equal key alist)), precondition check (assoc-equal key alist) \neq nil

```